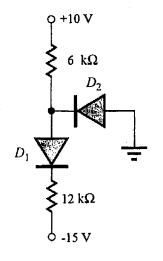

1. (12 pts) Find the Q-point for the diodes  $D_1$  and  $D_2$  shown in the figure below using the constant voltage drop (CVD) model with  $V_{on} = 1$  V. Give answers for **BOTH** diodes.

Assume both diodes are on.

$V_{0} = -V_{0} = -1V$   $V_{0} = -V_{0} = -1V$   $V_{0} = \frac{10V - (-1)V}{6k\Omega} = \frac{183mA}{12k\Omega}$   $I_{1} = \frac{(-1-1+1t)V}{12k\Omega} = \frac{108mA}{12k\Omega}$ I2= I1-1 = -0.75m/ 20 Inconsistent with BON'

DION - DIOFF

$$T = I_{1} = \frac{1047 - 15V}{(6 - 112) \text{ kg}} = 1.33 \text{ mA}$$

$$V_{0} = 10V - IR = 10 - 1.33 \text{ mA} \cdot \text{ leg} = 2V$$

$$V_{0} = -V_{0} = -2V$$

$$0 - pt \text{ for } D_{1} = (1.33 \text{ mA}, 1V)$$

$$Q \cdot pt \text{ for } D_{2} = (0A_{1} - 2V)$$

Chark IDIO, VA=Von, consisted with DION ID=0, Voz=-2V = Von, was start with DOFF

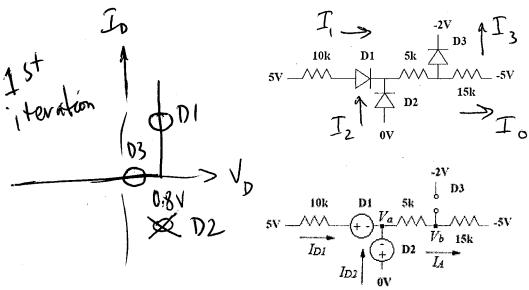

- 3. (25 points) In the following circuit, use the constant voltage diode model with a threshold (turn-on) voltage of 0.8 V. Assume the diodes  $D_1$  and  $D_2$  are on and the diode  $D_3$  is off.

- a) (5 pt) Calculate the voltage across each diode.

- b) (5 pt) Calculate the current through each diode.

- c) (5 pt) Check your assumptions for D<sub>1</sub> -- are they correct? Why or why not?

- d) (5 pt) Check your assumptions for D<sub>2</sub> -- are they correct? Why or why not?

- e) (5 pt) Check your assumptions for D<sub>3</sub> -- are they correct? Why or why not?

According to the assumption:  $V_{D1} = 0.8 \text{ V}$ ,  $V_{D2} = 0.8 \text{ V}$ ,  $I_{D3} = 0.8 \text{ V}$

$$V_a = -0.8 \text{ V}, \ I_{D1} = \frac{5 \text{ V} - 0.8 \text{ V} - (-0.8 \text{ V})}{10 \text{ k}\Omega} = 0.50 \text{ mA}.$$

$$I_A = \frac{0 \text{ V} - 0.8 \text{ V} - (-5 \text{ V})}{15 \text{ k}\Omega + 5 \text{ k}\Omega} = 0.21 \text{ mA}.$$

$$I_{D2} = I_A - I_{D1} = -0.29 \text{ mA}$$

$$V_b = V_a - 5 \text{ k}\Omega \cdot 0.21 \text{ mA} = -1.85 \text{ V}$$

$$V_{D3} = V_b - (-2 \text{ V}) = 0.15 \text{ V}$$

$D_1$ :  $V_{D1} = 0.8$  V,  $I_{D1} = 0.50$  mA.  $I_{D1} > 0$ , assumption for  $D_1$  being on is correct.

$D_2$ :  $V_{D2} = 0.8$  V,  $I_{D2} = -0.29$  mA.  $I_{D2} < 0$ , assumption for  $D_2$  being on is NOT correct.

D<sub>3</sub>:  $I_{D3} = 0$ ,  $V_{D3} = 0.15$  V < 0.8 V.  $V_{D3} < V_{on}$ , assumption for D<sub>3</sub> being off is correct.  $V_{D3} = 0.15$  V < 0.8 V.  $V_{D3} < V_{on}$ , assumption for D<sub>3</sub> being off is

$$V_{b} = -5V + T_{o} * 15kD , T_{o} = \frac{5V - V_{om} - (-5V)}{10k + 5k + 15k} = \frac{9.2V}{30kD}$$

$$= -5V + \frac{4.2V}{30kD} 15kD = 0.307 mA$$

$$= -5V + 4.6V = -0.4V$$

$$V_{03} = -0.4 - (-20) = 1.60 > V_{on} = 0.3$$

I, = 5V - Von - Vb = 5.4V

= 0.36 mA

$$V_b = -2V + bon = -1.2V$$

$$V_a = 5V - V_{on} = I_i(lokn)$$

$$= 5V - 0.8V - 3.6V = 0.6V$$

$$V_{D2} = 0 - 0.6V = -0.6V = > OFF$$

$$I_3 = I_1 - \frac{V_b - (-5V)}{15kR} = 0.36mA - \frac{3.8V}{15kR} = 0.36mA - 0.25mA$$

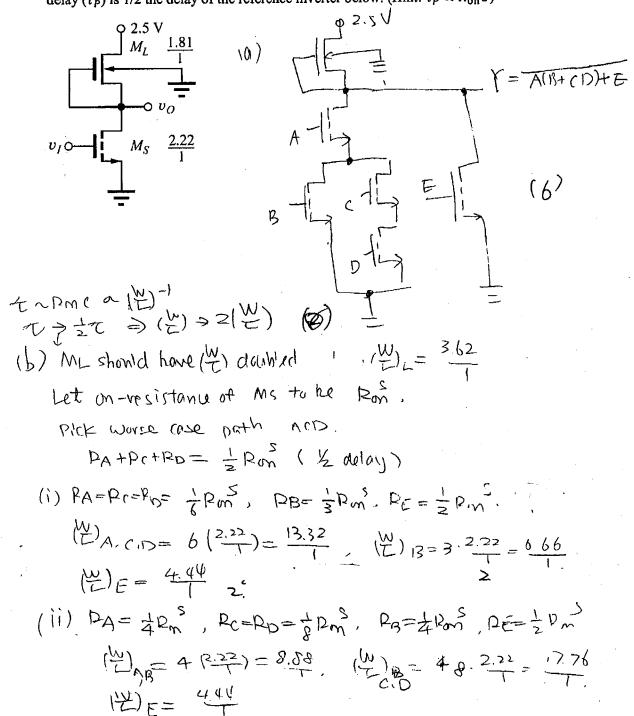

(16 pts) You are asked to design an NMOS logic gate that implements

$$Y = \overline{A(B + CD) + E}$$

based on the reference inverter shown below.

- (a) (6 pts) Draw the circuit diagram.

- (b) (10 pts) Find the W/L ratios of all transistors in the circuit such that the propagation delay  $(\tau_P)$  is 1/2 the delay of the reference inverter below. (Hint:  $\tau_P \propto R_{\rm on}C$ )