# Interconnections: Copper & Low K Dielectrics

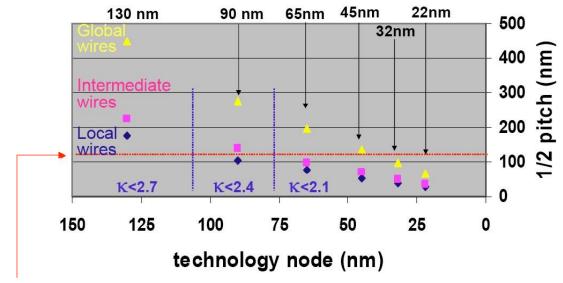

### **ITRS 2002 Interconnect Scaling Recommendations**

Narrow line effects

Ref: J. Gambino, IEDM Short Course, 2003

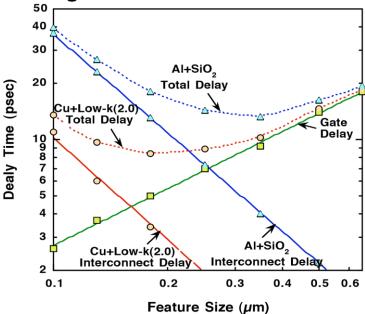

## **Interconnect Scaling Scenarios**

Scaling need for lower resistivity metal, Low-k

#### • Scale Metal Pitch and Height

- R and J increase by square of scaling factor

- Sidewall capacitance unchanged

- Aspect ratio for gapfill / metal etch unchanged

- Drives need for very low resistivity metal with significantly improved EM performance

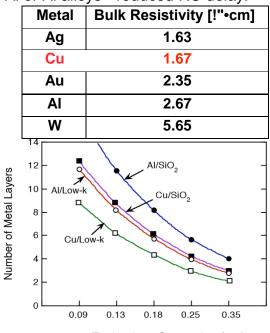

### Why Cu?

• Lower resistivity than AI or AI alloys - reduced RC delay.

Technology Generation (µm)

• Better electromigration reliability than Al alloys.

|                                                   | AI              | Cu              | 99.9 - 99 - 99 - 99 - 95 - 90 - 90 - 90 - 9                                                                                                                                                                                                                                                                           |

|---------------------------------------------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Melting Point                                     | 660 °C          | 1083 ºC         | 90<br>75<br>90<br>75<br>90<br>75<br>90<br>75<br>90<br>90<br>75<br>90<br>75<br>90<br>90<br>75<br>90<br>90<br>75<br>90<br>90<br>90<br>75<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90                                                                                                                    |

| E <sub>a</sub> for Lattice<br>Diffusion           | 1.4 eV          | 2.2 eV          |                                                                                                                                                                                                                                                                                                                       |

| E <sub>a</sub> for Grain<br>Boundary<br>Diffusion | 0.4 –<br>0.8 eV | 0.7 –<br>1.2 eV | 1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 .1 </th |

|                                                   |                 |                 | Stress Time (Hrs)                                                                                                                                                                                                                                                                                                     |

Ref: S. Luce, (IBM), IEEE IITC 1998

## **Challenges for Cu Metallization**

Limited processing methods: Introduction of Cu must be managed carefully.

- Obstacles

- Line patterning: Poor dry-etchability of Cu Poor adhesion to dielectrics

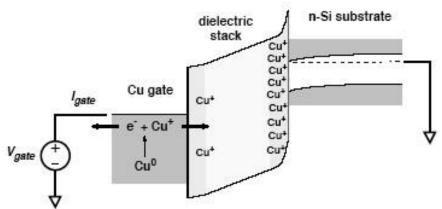

- Copper is very mobile in  $SiO_2 =>$  Contamination to Si Devices

- Increased leakage in SiO<sub>2</sub>

- Increased junction leakage

- Lower junction break down voltage

Cu atoms ionize, penetrate into the dielectric, and then accumulate in the dielectric as Cu+ space charge.

- Bias temperature stressing is employed to characterize behavior

- Both field and temperature affect barrier lifetime

- Neutral Cu atoms and charged Cu ions contribute to Cu transport through dielectrics

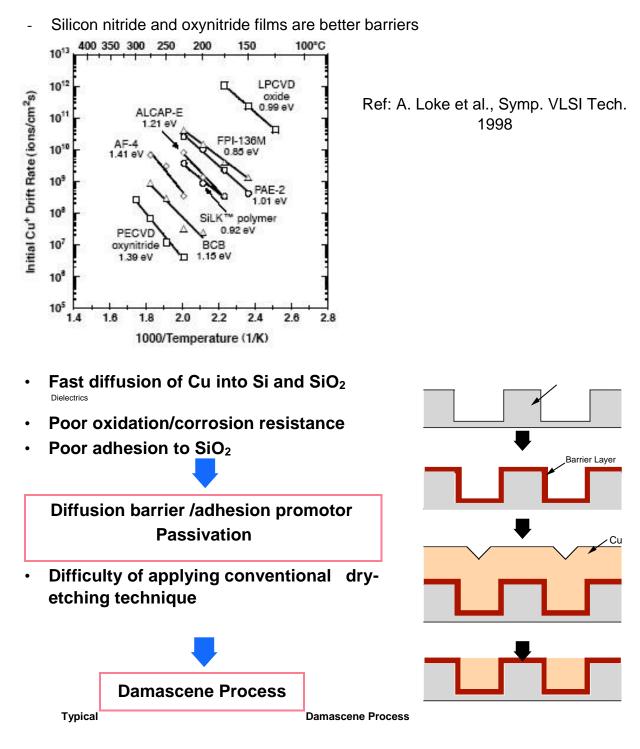

#### Solutions

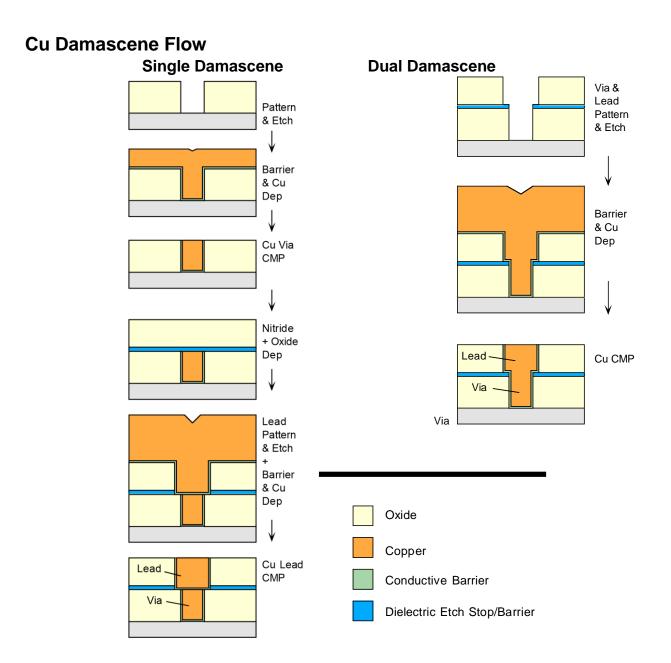

- Damascene process for patterning

- Using diffusion Barriers

- Liners TiN, TaN, etc

- Silicon Nitride, PSG

- •

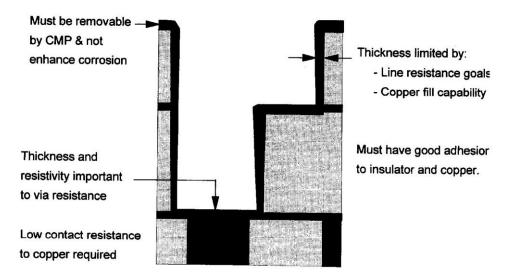

# **Barriers/Liners**

Barrier Requirements:

- Ultrathin films should be good barriers

- Low resistance

- Chemically stable

- Defect free to high temperatures

#### Barriers:

Transition metals (Pd, Cr, Ti, Co, Ni, Pt) generally poor barriers, due to high reactivities to Cu <450°C</li>

<u>Exception</u>: Ta, Mo, W ... more thermally stable, but fail due to Cu diffusion through grain boundaries (polycrystalline films)

- Transition metal alloys: Can be deposited as amorphous films (stable up to 500°C)

- Transition metal silicon compounds: Adding Si to Ta, Ti, Mo, W yields amorphous refractory barriers with stability to 700°C

- Amorphous ternary alloys: Very stable due to high crystallization temperatures (i.e., Ta<sub>36</sub>S<sub>14</sub>,N<sub>50</sub>, Ti<sub>34</sub>Si<sub>23</sub>N<sub>43</sub>)

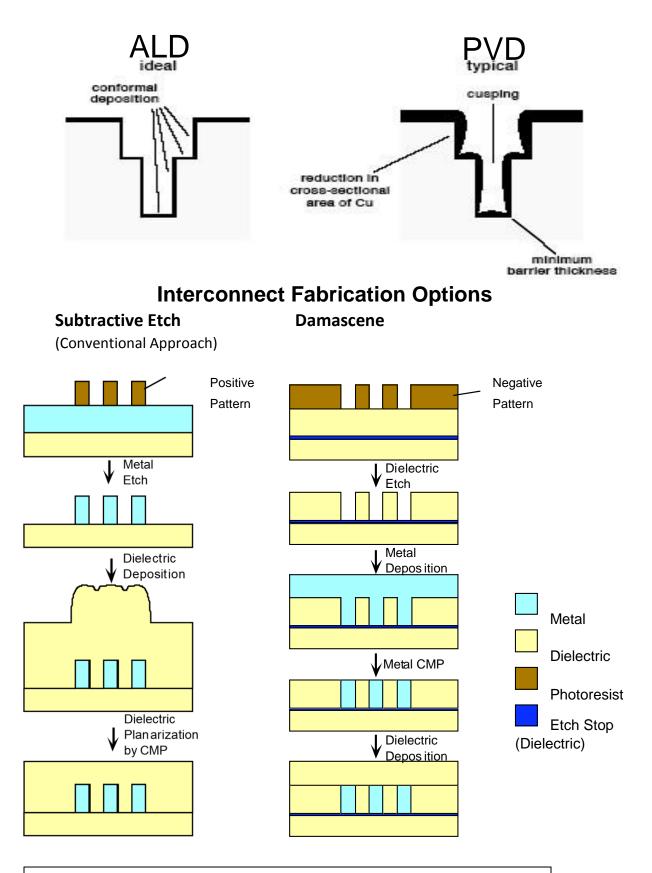

- Currently PVD (sputtering/evaporation is used primarily to deposit the barrier/liner, however, step coverage is a problem. ALD is being developed for barrier/liner application.

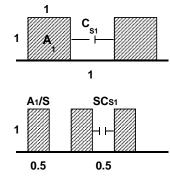

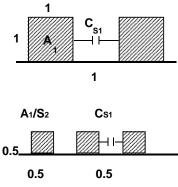

- Conventional approach of metal etch is used for AI

- Damascene approach is used for Cu as it can't be dry etched

# **Deposition methods**

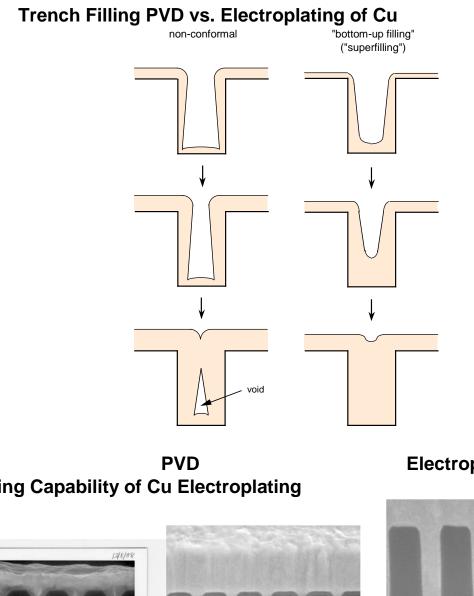

# Physical vapor deposition (PVD) : Evaporation, Sputtering

- conventional metal deposition technique: widely used for Al interconnects

- produce Cu films with strong (111) texture and smooth surface, in general

- poor step coverage: not tolerable for filling high-aspect ratio features

### Chemical vapor deposition (CVD) :

- conformal deposition with excellent step coverage in high-aspect ratio holes and vias

- costly in processing and maintenance

- generally produce Cu films with fine grain size, weak (111) texture and rough surface

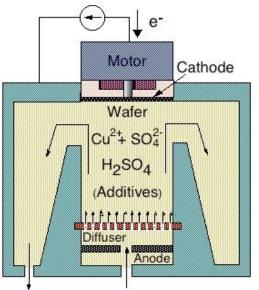

### **Electroplating System for Cu**

**Continuous Chemical Circulation**

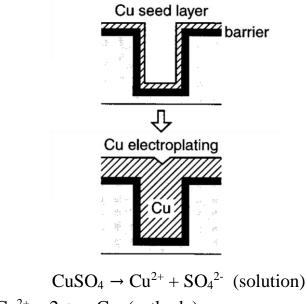

Dissociation:  $CuSO_4 \rightarrow Cu^{2+} + SO_4^{2-}$  (solution) Reduction:  $Cu^{2+} + 2e^- \rightarrow Cu$  (cathode) Oxidation:  $Cu \rightarrow Cu^{2+} + 2e^-$  (anode)

Direct electroplating on the barrier gives poor results. Therefore a thin layer of Cu is needed as a seed. It can be deposited by PVD, CVD or ALD.

<sup>B</sup>Good step coverage and filling capability comparable to CVD process (0.25 μm)

© Compatible with low-K dielectrics

- B Generally produce strong (111) texture of Cu film

- Produce much larger sized grain structure than any other deposition methods through self-annealing process

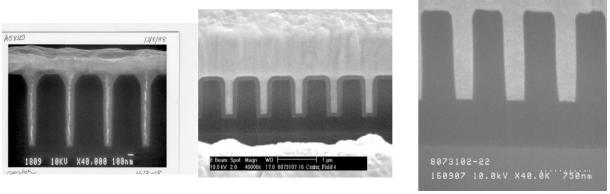

Filling Capability of Cu Electroplating

**Electroplating Trench**

- 0.13µ trenches

- 0.18µ vias

029µ vias

Ref: Jonathan Reid, IITC, 1999