## EE486 Integrated Circuit Fabrication Spring 2017

## Homework o Due in class on Monday, April 3, 2017.

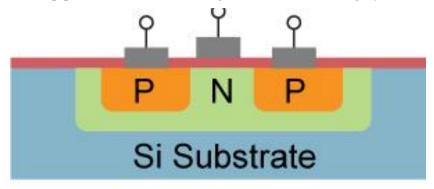

1. Describe a fabrication process to make the structure below. It is not necessary to provide any process details, just say for example "deposit oxide film" and "deposit, expose and develop photoresist." The red region is oxide and the grey is aluminum.

- 2. For the above structure, identify the diodes, bipolar transistors and MOSFETs present. Draw the resulting circuit diagram.

- 3. Consider a diffused silicon region doped with  $N_A=3\times 10^{18}\,\mathrm{cm}^{-3}$  and  $N_D=1\times 10^{18}\,\mathrm{cm}^{-3}$  to a depth of 40 nm in a wafer.

- a) What are the carrier concentrations and carrier mobilities in this region (you can use plot from posted 331 notes)?

- b) What is the resistivity of this region?

- c) If the diffused region is 2000 nm long and 50 nm wide, what would be the resistance?

- 4. Consider a silicon pn junction diode with area  $A=0.5~\mu m^2$ ,  $N_A=5\times 10^{18}~\rm cm^{-3}$  on the p-type side and  $N_D=2\times 10^{17}~\rm cm^{-3}$  on the n-type side. Use  $n_i=1.0\times 10^{10}~\rm cm^{-3}$ . Assume that the thickness of both the *p*-type region  $W_p{}'=50~\rm nm$  and the *n*-type region  $W_n{}'=20~\rm nm$  are smaller than the respective minority carrier diffusion lengths.

What is the reverse saturation current for this diode?