#### EE 212 FALL 1999-00

# SEMICONDUCTOR MANUFACTURING - CLEAN ROOMS, WAFER CLEANING AND GETTERING-Chapter 4

- Modern IC factories employ a three tiered approach to controlling unwanted impurities:

- 1. clean factories 2. wafer cleaning 3. gettering

| Year of 1st DRAM Shipment               | 1997        | 1999               | 2003        | 2006        | 2009        | 2012         |

|-----------------------------------------|-------------|--------------------|-------------|-------------|-------------|--------------|

| Minimum Feature Size                    | 250nm       | 180nm              | 130nm       | 100nm       | 70nm        | 50nm         |

| Wafer Diameter (mm)                     | 200         | 300                | 300         | 300         | 450         | 450          |

| DRAM Bits/Chip                          | 256M        | 1G                 | 4G          | 16G         | 64G         | 256G         |

| DRAM Chip Size (mm <sup>2</sup> )       | 280         | 400                | 560         | 790         | 1120        | 1580         |

| Microprocessor                          | 11M         | 21M                | 76M         | 200M        | 520M        | 1.40B        |

| Transistors/chip                        |             |                    |             |             |             |              |

| Critical Defect Size                    | 125nm       | 90nm               | 65nm        | 50nm        | 35nm        | 25nm         |

| Starting Wafer                          | 0.60        | 0.29               | 0.14        | 0.06        | 0.03        | 0.015        |

| Total LLS (cm <sup>-2</sup> )           |             |                    |             |             |             |              |

| DRAM GOI                                | 0.06        | 0.03               | 0.014       | 0.006       | 0.003       | 0.001        |

| <b>Defect Density (cm<sup>-2</sup>)</b> |             |                    |             |             |             |              |

| Logic GOI                               | 0.15        | 0.15               | 0.08        | 0.05        | 0.04        | 0.03         |

| <b>Defect Density (cm<sup>-2</sup>)</b> |             |                    |             |             |             |              |

| Starting Wafer                          | $3x10^{10}$ | 1x10 <sup>10</sup> | Under       | Under       | Under       | Under        |

| Total Bulk Fe (cm <sup>-3</sup> )       |             |                    | $1x10^{10}$ | $1x10^{10}$ | $1x10^{10}$ | $1x10^{10}$  |

| Critical Metals on                      |             | 0                  | 0           | 0           | 0           | 0            |

| Wafer Surface After                     | $5x10^9$    | 4x10 <sup>9</sup>  | $2x10^9$    | $1x10^9$    | $< 10^9$    | $< 10^9$     |

| Cleaning (cm <sup>-2</sup> )            |             |                    |             |             |             |              |

| Starting Material                       |             |                    |             |             |             |              |

| <b>Recombination Lifetime</b>           | ≥ 300       | ≥ 325              | ≥ 325       | ≥ 325       | ≥ 450       | ≥ <b>450</b> |

| (µsec)                                  |             |                    |             |             |             |              |

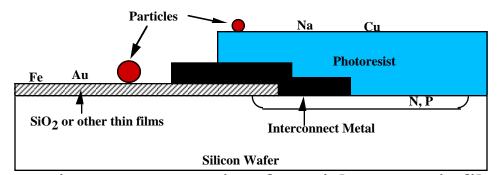

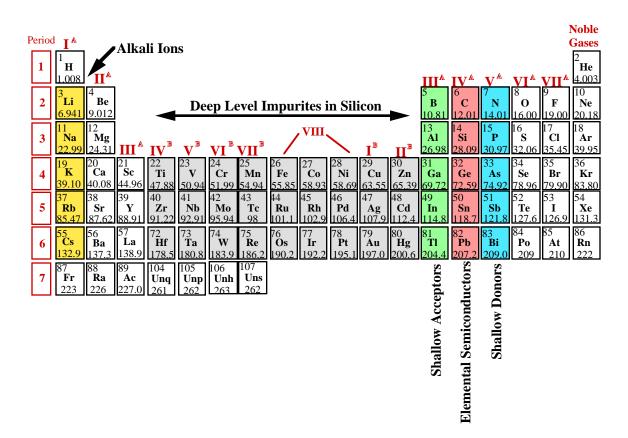

• Contaminants may consist of particles, organic films (photoresist), heavy metals or alkali ions.

2

Example #1: MOS  $V_{TH}$  is given by:

$$V_{TH} = V_{FB} + 2\phi_f + \frac{\sqrt{2\epsilon_S q N_A(2\phi_f)}}{C_O} + \frac{qQ_M}{C_O}$$

(1)

- If  $t_{ox}$  = 10 nm, then a 0.1 volt  $V_{th}$  shift can be caused by  $Q_M$  = 6.5 x  $10^{11}$  cm<sup>-2</sup> (< 0.1% monolayer or 10 ppm in the oxide).

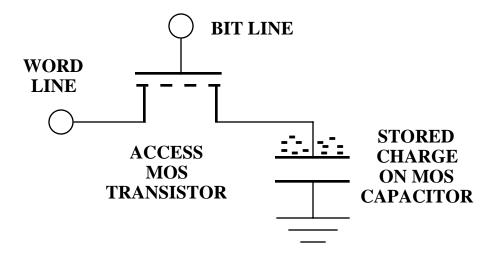

- Example #2: MOS DRAM

• Refresh time of several msec requires a generation lifetime of

$$\tau_{\rm G} = \frac{1}{\sigma v_{\rm th} N_{\rm t}} \approx 25 \; \mu {\rm sec} \qquad (2)$$

• This requires  $N_t \approx 10^{12} \ cm^{-3} \ or \approx 0.02 \ ppb$  (see text).

3

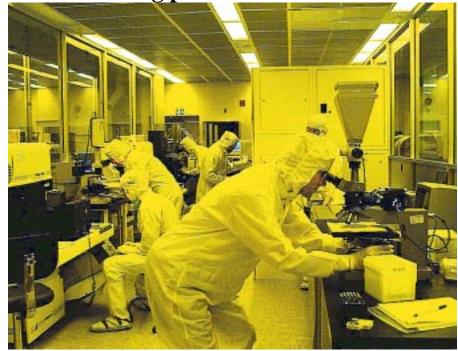

#### **Level 1 Contamination Reduction: Clean Factories**

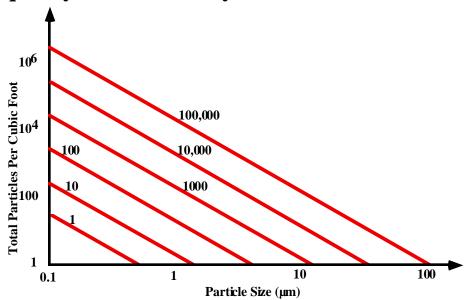

• Air quality is measured by the "class" of the facility.

- Factory environment is cleaned by:

- Hepa filters and recirculation for the air,

- "Bunny suits" for workers.

- Filtration of chemicals and gases.

- Manufacturing protocols.

4

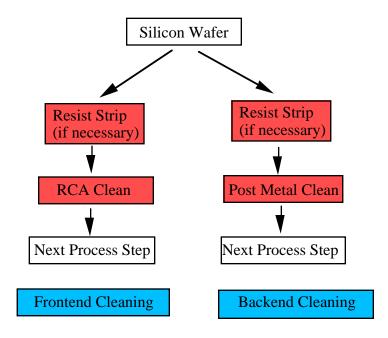

**Level 2 Contamination Reduction: Wafer Cleaning**

• RCA clean is "standard process" used to remove organics, heavy metals and alkali ions.

5

• Ultrasonic agitation is used to dislodge particles.

6

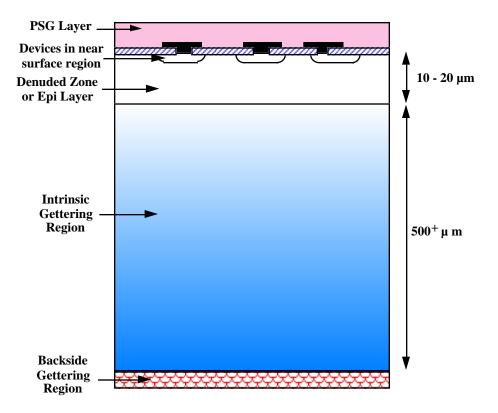

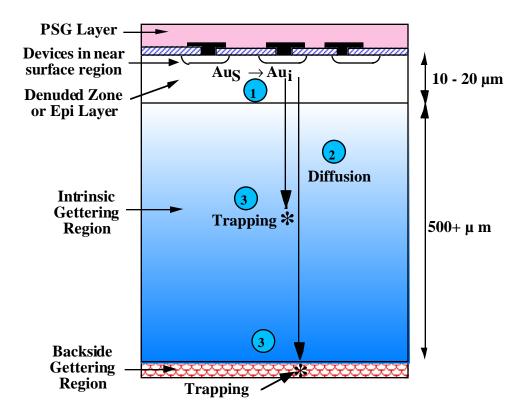

### **Level 3 Contamination Reduction: Gettering**

• Gettering is used to remove metal ions and alkali ions from device active regions.

- For the alkali ions, gettering generally uses dielectric layers on the topside (PSG or barrier Si<sub>3</sub>N<sub>4</sub> layers).

- For metal ions, gettering generally uses traps on the wafer backside or in the wafer bulk.

- Backside = extrinsic gettering.

- Bulk = intrinsic gettering.

7

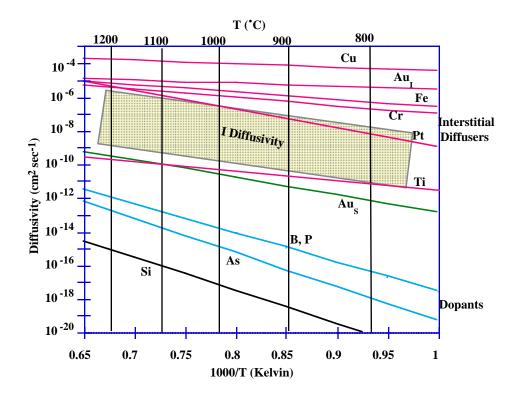

- Heavy metal gettering relies on the facts that:

- Metals diffuse very rapidly in silicon.

Metals segregate to "trap" sites.

8

• "Trap" sites can be created by SiO<sub>2</sub> precipitates (intrinsic gettering), or by backside damage (extrinsic gettering).

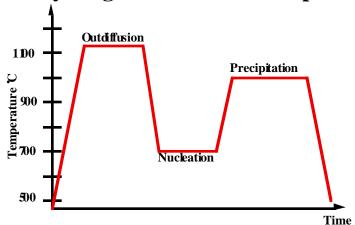

• In intrinsic gettering, CZ silicon is used and SiO<sub>2</sub> precipitates are formed in the wafer bulk through temperature cycling at the start of the process.

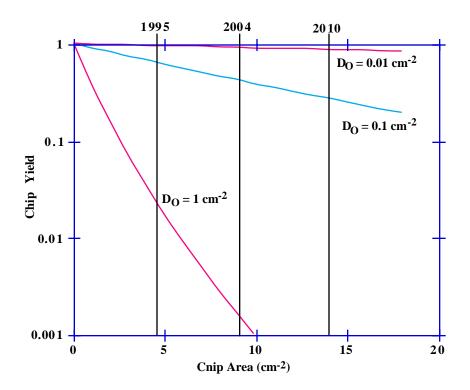

**Modeling Particle Contamination and Yield**

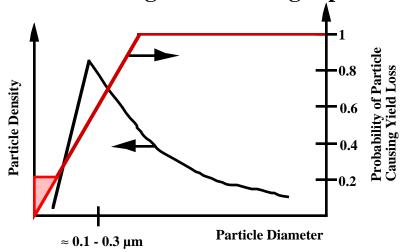

- $\approx 75\%$  of yield loss in modern VLSI fabs is due to particle contamination.

- Yield models depend on information about the distribution of particles.

- Particles on the order of 0.1 0.3  $\mu m$  are the most troublesome:

- larger particles precipitate easily

- smaller ones coagulate into larger particles

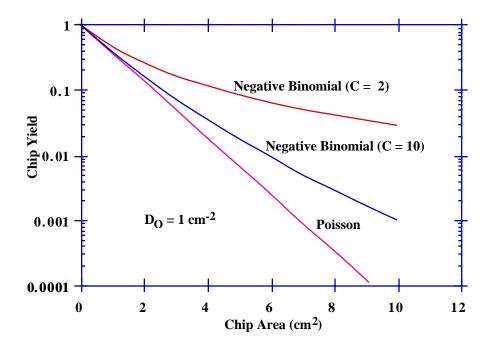

• Yields are described by Poisson statistics in the simplest case:

$$Y = \exp^{-A_C D_O}$$

(3)

9

where  $A_C$  is the critical area and  $D_O$  is the defect density.

- This model assumes independent randomly distributed defects and often underpredicts yields.

- Negative binomial statistics eliminates these assumptions and is more accurate.

$$Y = \frac{1}{\left(1 + \frac{A_C D_O}{C}\right)^C}$$

(4)

where C is a measure of the particle spatial distribution (clustering factor).

• Note that defect densities will need to be extremely small in the future.

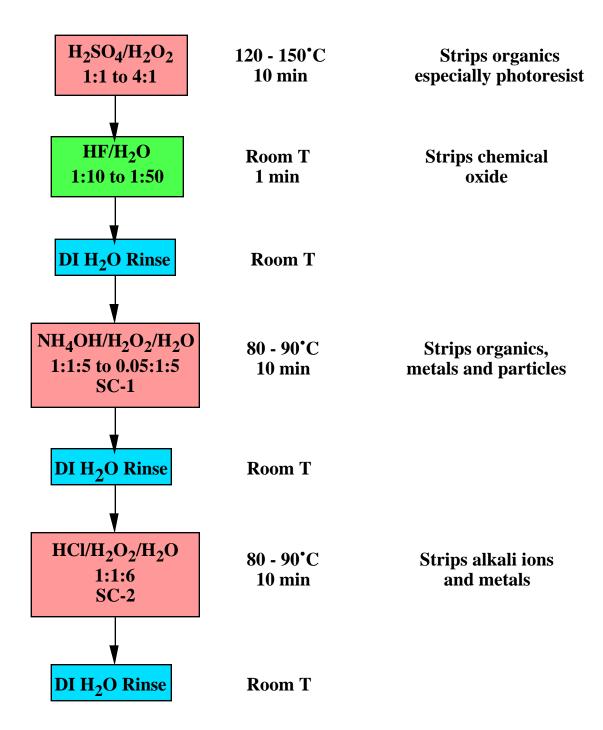

## **Modeling Wafer Cleaning**

- Cleaning involves removing particles, organics (photoresist) and metals from wafer surfaces.

- Particles are largely removed by ultrasonic agitation during cleaning.

- Organics like photoresists are removed in an O<sub>2</sub> plasma or in H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub> solutions.

- The "RCA clean" is used to remove metals and any remaining organics.

- Metal cleaning can be understood in terms of the following chemistry.

$$Si + 2H_2O \leftrightarrow SiO_2 + 4H^+ + 4e^-$$

(5)

$$\mathbf{M} \leftrightarrow \mathbf{M}^{\mathbf{z}^+} + \mathbf{z}\mathbf{e}^- \tag{6}$$

• If we have a water solution with a Si wafer and metal atoms and ions, the stronger reaction will dominate.

- Generally (6) is driven to the left and (5) to the right so that SiO<sub>2</sub> is formed and M plates out on the wafer.

- Good cleaning solutions drive (6) to the right since M<sup>+</sup> is soluble and will be desorbed from the wafer surface.

| Oxidant/<br>Reductant | Standard<br>Oxidation | Oxidation-Reduction Reaction                           |

|-----------------------|-----------------------|--------------------------------------------------------|

|                       | Potential (volts)     |                                                        |

| Mn <sup>2+</sup> /Mn  | 1.05                  | $Mn \leftrightarrow Mn^{2+} + 2e^{-}$                  |

| SiO <sub>2</sub> /Si  | 0.84                  | $Si + 2H_2O \leftrightarrow SiO_2 + 4H^+ + 4e^-$       |

| Cr <sup>3+</sup> /Cr  | 0.71                  | $Cr \leftrightarrow Cr^{3+} + 3e^{-}$                  |

| Ni <sup>2+</sup> /Ni  | 0.25                  | $Ni \leftrightarrow Ni^{2+} + 2e^{-}$                  |

| Fe <sup>3+</sup> /Fe  | 0.17                  | $Fe \leftrightarrow Fe^{3+} + 3e^{-}$                  |

| $H_2SO_4/H_2SO_3$     | -0.20                 | $H_2O + H_2SO_3 \leftrightarrow H_2SO_4 + 2H^+ + 2e^-$ |

| Cu <sup>2+</sup> /Cu  | -0.34                 | $Cu \leftrightarrow Cu^{2+} + 2e^{-}$                  |

| $O_2/H_2O$            | -1.23                 | $2H_2O \leftrightarrow O_2 + 4H^+ + 2e^-$              |

| Au <sup>3+</sup> /Au  | -1.42                 | $Au \leftrightarrow Au^{3+} + 3e^{-}$                  |

| $H_2O_2/H_2O$         | -1.77                 | $2H_2O \leftrightarrow H_2O_2 + 2H^+ + 2e^-$           |

| $O_3/O_2$             | -2.07                 | $O_2 + H_2O \leftrightarrow O_3 + 2H^+ + 2e^-$         |

- The strongest oxidants are at the bottom (H<sub>2</sub>O<sub>2</sub> and O<sub>3</sub>). These reactions go to the left grabbing e<sup>-</sup> and forcing (6) to the right.

- Fundamentally the RCA clean works by using  $H_2O_2$  as a strong oxidant.

## **Modeling Gettering**

- Gettering consists of:

- 1. Making metal atoms mobile.

- 2. Migration of these atoms to trapping sites.

- 3. Trapping of atoms.

• 1 generally happens by kicking out the substitutional atom into an interstitial site. One possible reaction is:

$$\mathbf{A}\mathbf{u}_{\mathbf{S}} + \mathbf{S}\mathbf{i}_{\mathbf{I}} \leftrightarrow \mathbf{A}\mathbf{u}_{\mathbf{i}}$$

(7)

- 2 usually happens easily once the metal is interstitial since most metals diffuse rapidly in this form.

- 3 happens because heavy metals segregate preferentially to damaged regions or to  $N^+$  regions or pair with effective getters like P (AuP pairs). (See Chapter 4.)

- In intrinsic gettering, the metal atoms segregate to dislocations around SiO<sub>2</sub> precipitates.